Chapter 5

Performance Analysis

•Definitions:

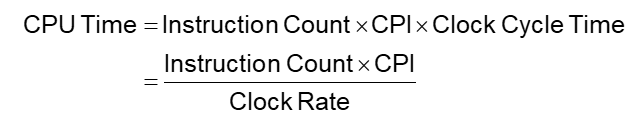

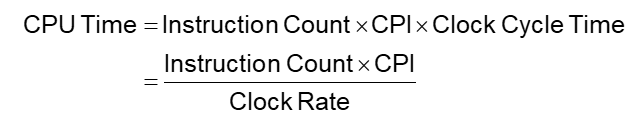

–CPI: Cycles per instruction

–clock period: seconds/cycle

–IPC: instructions per cycle

Throughput vs Response Time

•Response time (execution time) – the time between the start and the completion of a task

–Important to individual users

•Throughput (bandwidth) – the total amount of work done in a given time

–Important to data center managers

CPU Time

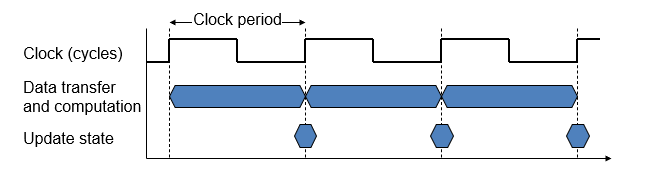

CPU Clocking

Clock period(周期): duration of a clock cycle

250ps = 0.25ns = 250×10–12s

Clock frequency (频率): cycles per second

4.0GHz = 4000MHz = 4.0×109Hz

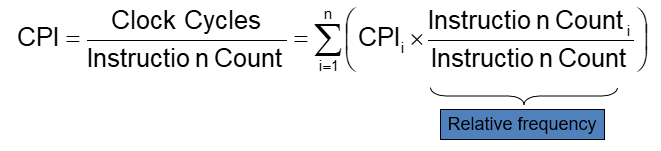

Instruction Count and CPI

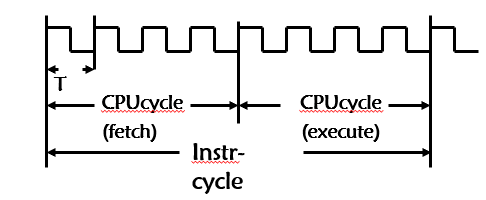

Weighted average CPI

e.g

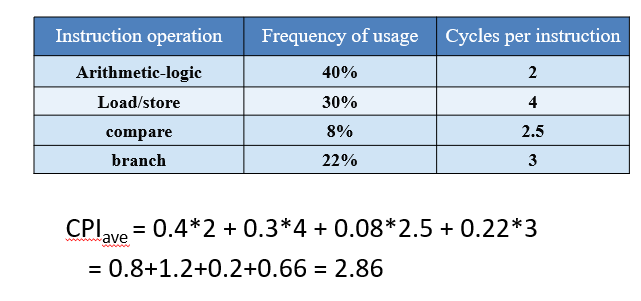

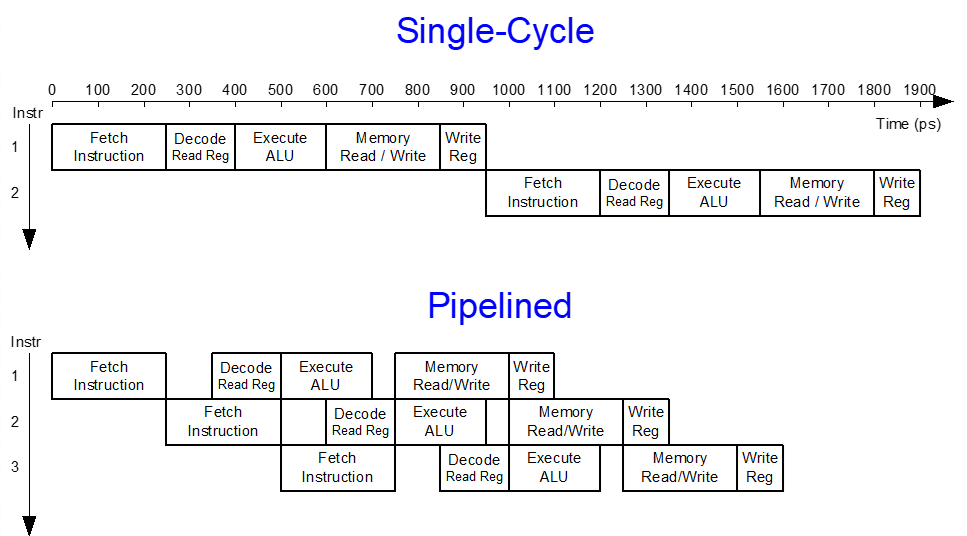

Single-Cycle Processor

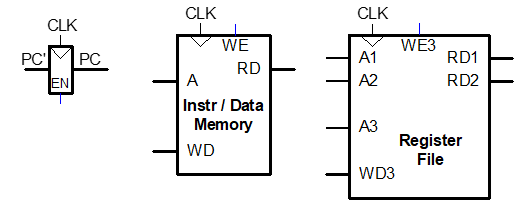

state elements

PC: program counter

I type

Multicycle Processor

What’s improved

read, write or alu operation in one cycle

每个周期内,完成一次read或write操作,或ALU操作;

different instruction adopts different cycle combination

不同指令使用不同的周期组合;

only one adder and one memory, shared in different cycles

仅需要一个adder,在不同周期重复使用;

一个memory, 在不同周期使用.

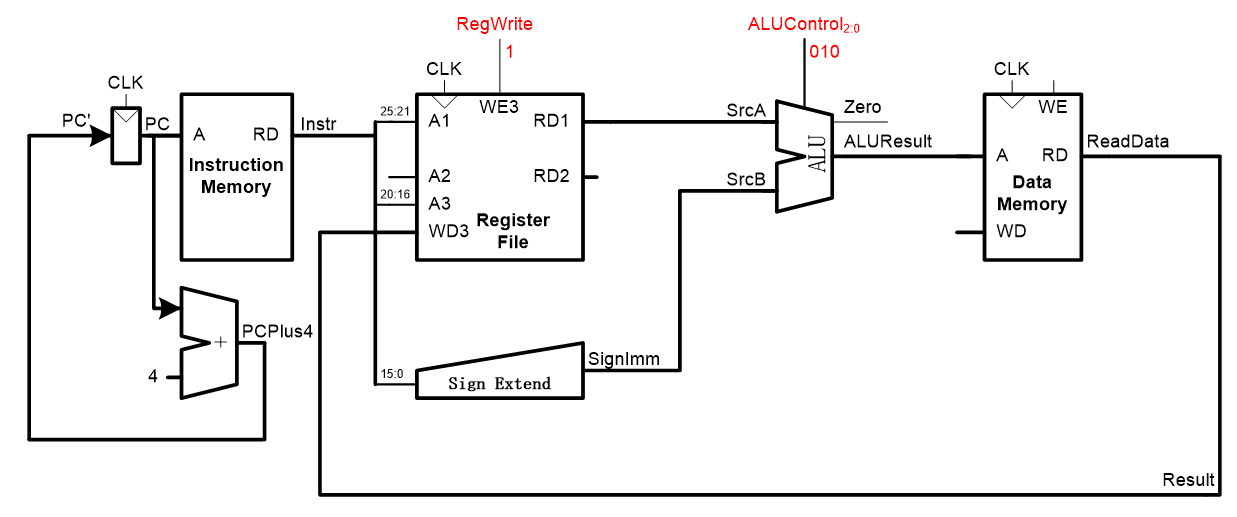

Instruction cycle

machine cycle(CPU周期)

State Elements

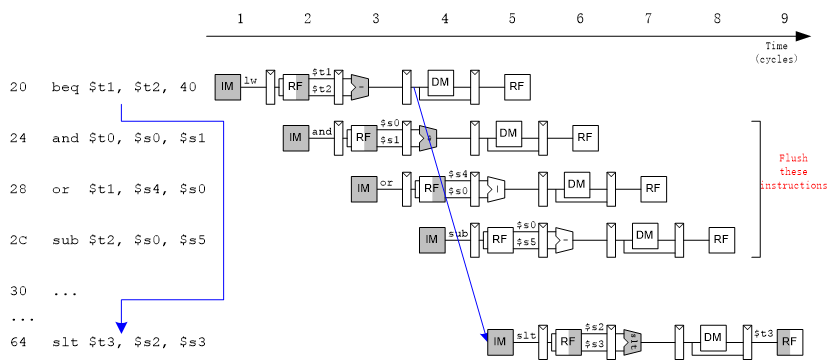

Pipelined Processor

•Divide single-cycle processor into 5 stages:

–Fetch

–Decode

–Execute

–Memory

–Writeback

Pipelined Processor Abstraction

(there is no building block conflict)

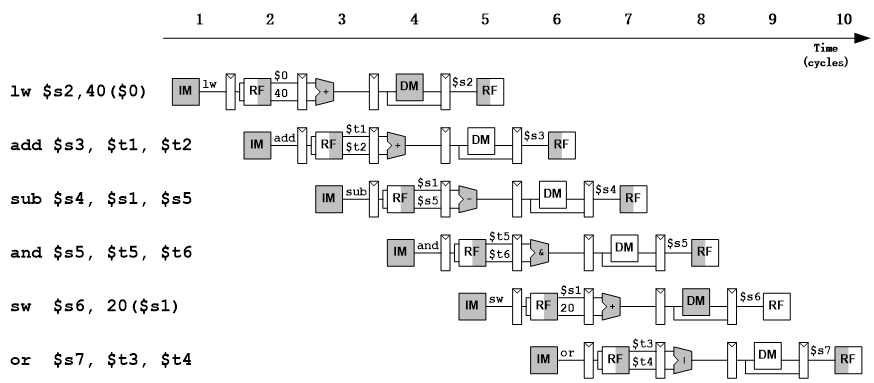

Pipelined Datapath

Same control unit as single-cycle processor

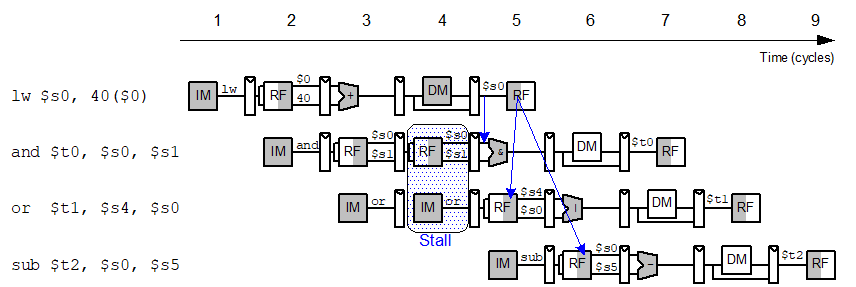

Harzard

Data hazard:

register value not yet written back to register file

Data forwarding

Stalling

Control Harzard

next instruction not decided yet (caused by branches)