Chapter 3

Sequential Logic Circuits

- Give sequence to events

- Have memory(short-term)

- Use feedback from output to input to store information

State Elements

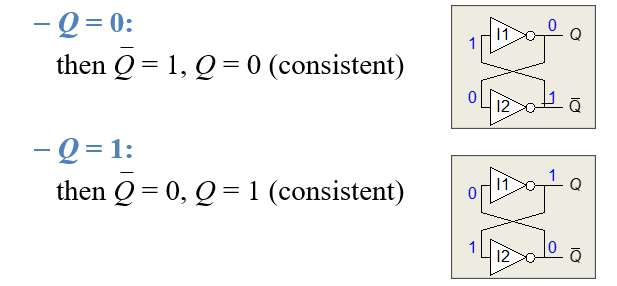

- Bistable circuit

- SR Latch

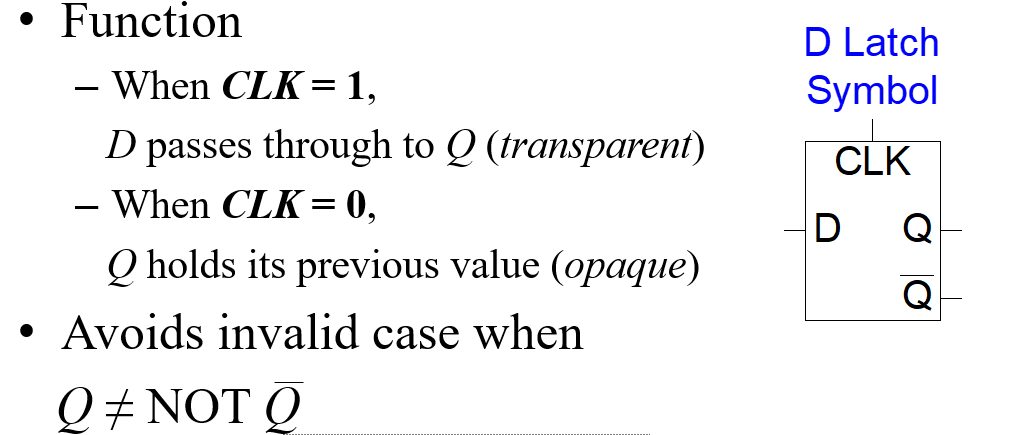

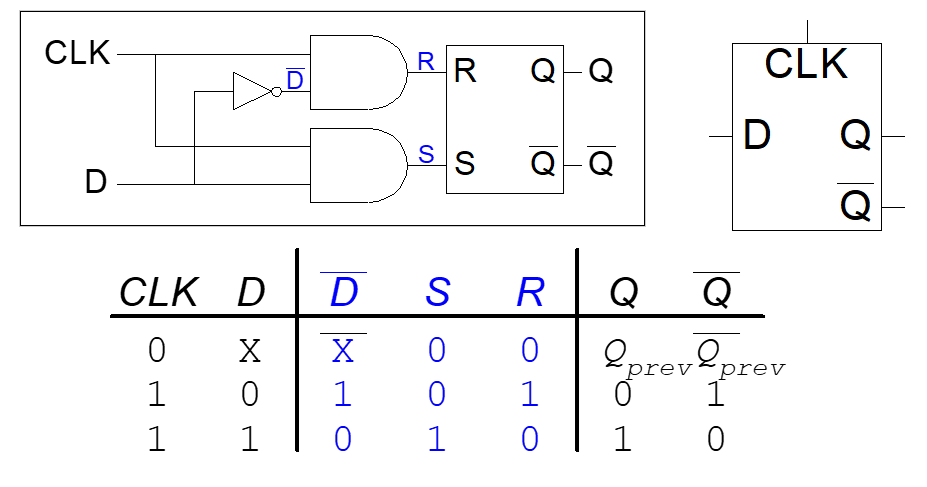

- D Latch

- D Flip-flop

Latch and Flip-flop

Bistable Circuit

SR Latch

D Latch

(Split value and time)

D Latch internal circuit

D Flip-Flop

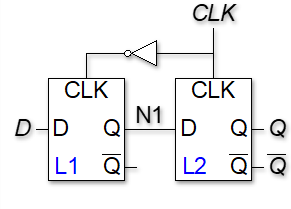

D Flip-Flop Internal Circuit

When CLK = 0

- L1 is transparent

- L2 is opaque

- D passes through N1

When CLK = 1

- L1 is opaque

- L2 is transparent

- N1 passes through to Q

THUS, on the edge of the clock (when CLK rises from 0 to1 ), D passes through to Q.

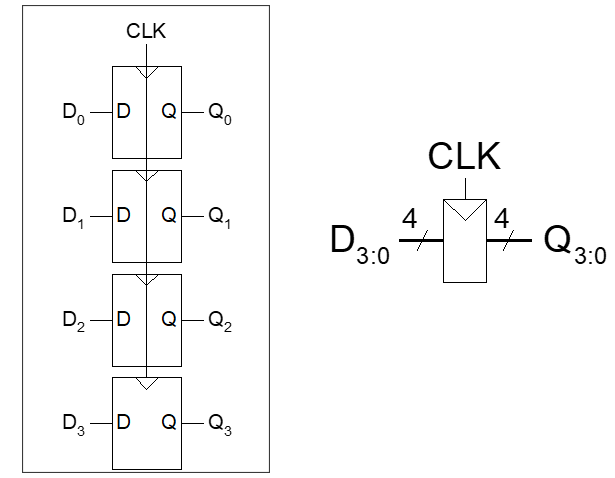

Registers

Enabled Flip-Flops

Inputs: CLK , D, EN

- EN = 1 : D passes through to Q on the clock edge

- EN = 0 : the flip-flop remains its previous state

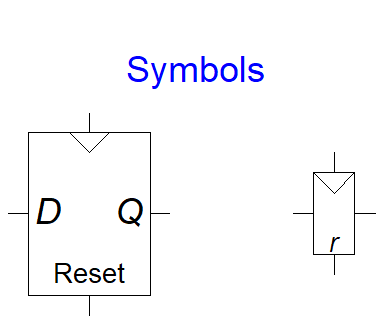

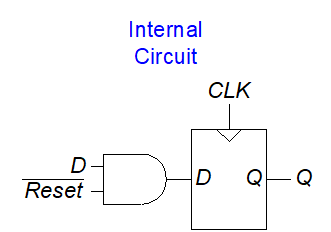

Resettable Flip-Flops

Two types:

- Synchronous : resets at the edge only

- Asynchronous : resets immediately when Reset = 1

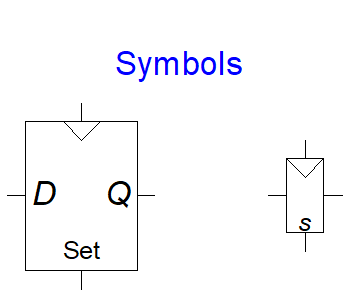

Settable Flip-Flops

Inputs : CLK, D, Set

- Set = 1 : Q is set to 1

- Set = 0: the flip-flop behaves as ordinary D flip-flop

-

Synchronous Sequential Logic Design

Rules of synchronous sequential circuit:

- Every circuit element is either a register or a combinational circuit

- At least one circuit element is a register

- All registers receive the same clock signal

- Every cyclic path contains at least one register

Two common synchronous sequential circuits

- Finite State Machines (FSMs)

- Pipelines

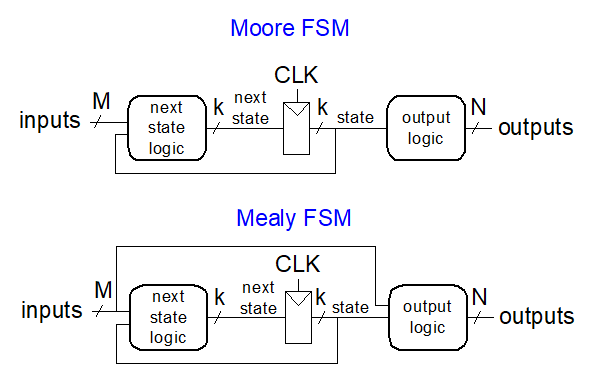

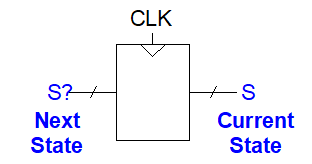

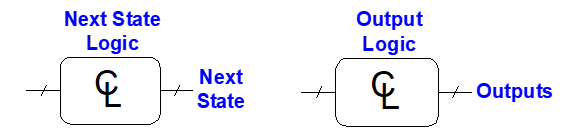

Finite State Machine (FSM)

Consists of:

- State Register

- Combinational Logic

Types

- Moore FSM : Outputs depend only on current state

- Mealy FSM : Outputs depend on current state and inputs